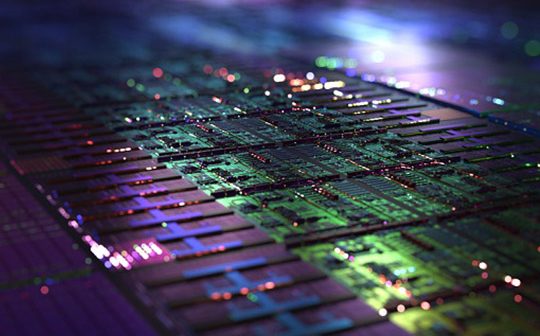

The technological pursuit of this decade may well be debunking Moore’s Law, and semiconductor manufacturers are competing for a front-row ticket, finds GlobalData.

Kiran Raj, Practice Head of Disruptive Tech at GlobalData, comments: “Moore’s Law, which states that the maximum number of transistors on a silicon chip doubles about every two years, has become a concept of the past. This was reflected in IBM’s introduction of disruptive 2 nanometers (nm) chip technology in 2021. The quest to lower nanometers in semiconductors is paving way for a new era of chip manufacturing.”

Abhishek Paul Choudhury, Senior Disruptive Tech Analyst at GlobalData, comments: “At present, the conventional length of transistors is 10 nanometers, and leading businesses have achieved 5 nm or 7 nm chips using cutting-edge research. Semiconductor manufacturers are now pursuing gate-all-around (GAA) architecture technology, which improves electrostatic characteristics, optimizes chip design, increases performance, and reduces power consumption.”

GlobalData’s latest Innovation Radar report, “Sand to silicon: how semiconductors are reimagining the digital future,” highlights how key technology companies are accelerating the development of chips in the semiconductor industry.

SMIC

Chinese Semiconductor Manufacturing International Corporation (SMIC) developed a quasi-7 nm process for chip manufacture. The chip is specifically created and fabricated for mining the Bitcoin cryptocurrency. The US sanctions in place with the impending trade war with China mean that SMIC’s progress of the 7 nm process can have significant impacts on East Asia.

Samsung

South Korean Samsung Electronics (Samsung) innovated a 3 nm process node using gate-all-around field-effect transistor (GAAFET) architecture. Its process uses nanosheets with broader channels, enabling higher performance and energy efficiency. The channel width of the nanosheet can be modified using the 3 nm GAA technology to optimize power consumption and performance based on client requirements. The consumer tech giant claims that the optimized 3 nm process can offer up to a 45% reduction in power consumption.

IBM

American big-tech International Business Machines (IBM) engineered a 2 nm chip that improves chip performance and energy efficiency. The chip can place up to 50 billion transistors on a chip the size of a fingernail. With more transistors on a chip, processor designers would have more options to incorporate core-level improvements to increase capabilities for applications like AI and cloud computing. It also provides new paths for hardware-enforced security and encryption.

Choudhury concludes: “With a continuously innovating and evolving semiconductor business landscape, it is reasonable to say that the race to lower nanometers in semiconductors should not be overlooked.”